这是一个非常好的问题,也是理解现代处理器架构的核心之一,说“ARM处理器IPC性能不行”其实是一个过于简化的说法,更准确的说法是:在传统的、以x86为代表的复杂指令集架构下,ARM的IPC性能曾经或在某些场景下确实存在差距,但这并非其设计的初衷,并且ARM正在通过多种方式弥补甚至超越这一差距。

下面我们来详细拆解这个问题,从几个层面来理解“为什么会有这种印象”以及“真实情况是怎样的”。

第一部分:理解什么是IPC?

IPC (Instructions Per Cycle),即“每周期执行指令数”,它是衡量处理器执行效率的关键指标,一个时钟周期内,CPU能完成多少条指令的执行。

一个重要的公式:

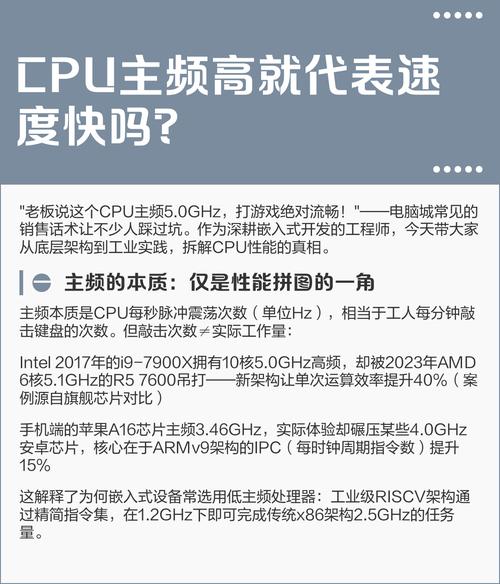

CPU性能 = IPC × 主频

这个公式告诉我们,CPU的性能由两个因素决定:

- IPC (效率):设计有多巧妙,流水线有多流畅。

- 主频 (速度):时钟能跑多快。

一个高IPC的CPU,即使主频不高,也可能比一个低IPC高主频的CPU快。

第二部分:为什么ARM的IPC“看起来”不行?(历史原因和架构差异)

这个印象主要源于PC和服务器领域,长期以来被x86处理器主导,与x86相比,ARM的架构设计哲学不同,导致其在IPC上的表现有差异。

CISC vs RISC 的设计哲学差异

这是最根本的原因。

- x86 (CISC - Complex Instruction Set Computer):

- 设计思想:指令集复杂,一条指令可以完成非常复杂的操作(一条指令就能完成内存到内存的数据搬运和算术运算)。

- 对IPC的影响:由于指令本身很复杂,解码和执行一条指令需要多个时钟周期,这拉低了单条指令的IPC,但好处是,程序员可以用更少的指令完成同样的任务,所以程序的总指令数较少,这是一种“用空间换时间”的设计。

- ARM (RISC - Reduced Instruction Set Computer):

- 设计思想:指令集精简,每条指令都简单、规整,通常在一个时钟周期内就能完成,所有复杂操作都需要通过简单的指令组合来实现。

- 对IPC的影响:由于指令简单,单条指令的执行效率高,单条指令的IPC理论上可以更高,但缺点是,完成同一个任务,需要执行更多的指令,程序的总指令数较多,这是一种“用时间换空间”的设计。

打个比方:

- x86 像一个瑞士军刀,功能强大,一把刀就能搞定很多事,但这把刀很复杂,打开它需要时间。

- ARM 像一整套螺丝刀,每把螺丝刀都简单高效,但你要拧一个复杂的螺丝,可能需要换好几次刀头。

在早期,由于ARM的指令集简单,为了完成同样的任务,它需要执行更多的指令,虽然单条指令快,但总体的“吞吐量”并不一定占优。

微架构的实现差异

除了指令集哲学,实际的产品设计(微架构)也决定了IPC的上限。

- x86 (以Intel/AMD为例):

- “大力出奇迹”:为了弥补CISC指令的解码开销和提升IPC,x86处理器投入了巨大的晶体管资源去构建极其复杂的乱序执行引擎、巨大的缓存和深度的分支预测。

- 结果:虽然单条指令效率低,但通过乱序执行,CPU可以“看”到未来,把没有依赖关系的指令重新排列组合,填满所有执行单元,从而在宏观上获得很高的指令吞吐量,这使得x86的IPC可以达到很高的水平(gt;2)。

- ARM (以苹果A/M系列、高通骁龙等为例):

- “精打细算”:ARM本身只设计IP核(核的蓝图),具体产品由各厂商(苹果、高通、三星等)自己实现,早期移动端的核心诉求是能效,而不是极致的性能。

- 结果:厂商在设计时,会权衡性能和功耗,复杂的乱序执行引擎和巨大缓存非常耗电,早期的ARM移动处理器在乱序执行的宽度和深度上,不如顶级的x86处理器,导致其IPC天花板相对较低。

主频的差异

很长一段时间里,x86处理器的主频远超ARM处理器。

性能 = IPC × 主频即使ARM的IPC和x86差距不大,但x86的主频高出一大截,最终性能也会碾压,这也是为什么当年的酷睿2、奔腾4等CPU频率能轻松上4GHz,而手机CPU长期在1-2GHz徘徊。

第三部分:现实情况正在改变——ARM的逆袭

近年来,情况发生了翻天覆地的变化,尤其是在苹果的带领下,ARM在IPC和整体性能上已经实现了对x86的超越。

架构的融合:RISC的进化与CISC的简化

现代的RISC和CISC已经没有严格的界限了。

- ARM RISC-V:现代ARM处理器虽然指令集是RISC,但其内部都包含了复杂的乱序执行、分支预测、超标量等机制,这些都是传统CISC处理器的强项,这使得ARM处理器的IPC可以做得非常高。

- x86 RISC化:现代x86处理器内部,复杂的CISC指令在被执行前,会被一个解码器翻译成若干条简单的、类似RISC的“微操作”(μops),然后CPU乱序执行这些μops,可以说,现代x86的内部核心也是一个RISC引擎,只是对外保留了CISC的指令集接口。

苹果的“降维打击”

苹果是改变游戏规则的关键,其自研的M系列芯片证明了ARM架构在极致性能上的潜力:

- 巨大的执行宽度:M1/M2/M3芯片拥有非常宽的乱序执行核心,可以同时发射和完成大量指令,极大地提升了IPC。

- 统一内存架构:CPU和GPU共享同一块内存,消除了数据搬运的瓶颈,让CPU的执行单元能更高效地工作。

- 能效比的极致追求:苹果通过精心的架构设计和先进的制程工艺,实现了在相同功耗下,提供远超x86的性能,或者在相同性能下,功耗远低于x86,这得益于其极高的IPC和优秀的能效设计。

M系列芯片的IPC性能已经可以媲美甚至超越同期的x86处理器,这是不争的事实。

服务器市场的发力

亚马逊的Graviton系列、Ampere的Altra等ARM服务器CPU,也证明了ARM在高性能计算领域的潜力,它们通过高核心数(比如64核、128核)和不错的单核IPC(得益于现代乱序执行架构),在云服务器等特定负载场景下,提供了极具竞争力的性价比和能效比。

回到最初的问题:“为啥ARM处理器IPC性能不行?”

- 历史原因:由于RISC设计哲学和早期移动端对能效的极致追求,ARM处理器在乱序执行等复杂微架构的实现上不如x86,导致其IPC上限较低。

- 误解来源:人们习惯用x86的“高性能”标准来衡量ARM,而忽略了两者最初的设计目标和市场定位不同。

- 现实改变:现代ARM处理器(尤其是苹果M系列)已经通过实现极其强大的乱序执行架构,大幅提升了IPC,甚至在某些方面超越了x86,其性能优势更多体现在能效比上,即用更少的电做更多的事。

“ARM处理器IPC性能不行”是一个过时且不准确的刻板印象。现代高性能ARM处理器的IPC已经非常强大,其真正的核心竞争力在于将高IPC与极致的能效比完美结合。