这是一个在 FPGA 领域非常经典且重要的处理器,我会从以下几个方面为你进行全面的解读:

(图片来源网络,侵删)

- 什么是 MicroBlaze?

- 核心特性与优势

- 工作原理:如何构建一个基于 MicroBlaze 的系统?

- 应用场景

- 与 RISC-V 的对比

什么是 MicroBlaze?

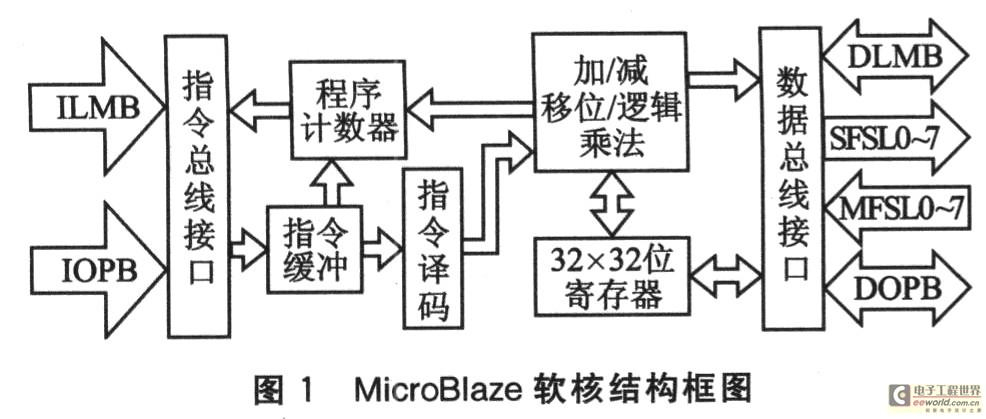

MicroBlaze 是由 AMD Xilinx(原赛灵思)公司开发的一款可配置的、32位 RISC 指令集架构 的软核处理器。

关键点解读:

- 软核处理器:这是它与 ARM、Intel 等硬核处理器的最大区别,MicroBlaze 的处理器逻辑不是固化在 FPGA 芯片硅片上的,而是以 HDL(硬件描述语言,如 Verilog 或 VHDL)的形式提供的,开发者可以将这个 HDL 代码综合成 FPGA 内的逻辑门电路,从而在 FPGA 内部“构建”出一个处理器。

- 可配置:开发者可以根据应用需求,自由地裁剪和定制 MicroBlaze 的功能,是否需要浮点运算单元?是否需要特定的硬件乘法器?是否需要调试接口?都可以在 Vivado 或 Vitis IDE 中进行配置。

- 32位 RISC:它遵循经典的 RISC(精简指令集计算机)设计原则,拥有简洁的指令集,这使得它在 FPGA 中占用逻辑资源相对较少,执行效率高。

核心特性与优势

MicroBlaze 的设计理念使其在特定领域具有无可比拟的优势。

优势:

-

高度灵活性:

(图片来源网络,侵删)

(图片来源网络,侵删)- 定制化:可以精确选择所需的指令和功能,移除不需要的部分,最小化逻辑占用和功耗。

- 系统集成:可以轻松地将 MicroBlaze 与其他 FPGA 硬件模块(如 DMA 控制器、定时器、UART、以太网 MAC、自定义加速器等)无缝集成在一个 FPGA 芯片内,实现片上系统。

-

低成本:

- FPGA 芯片本身比高端 SoC(System on Chip,如包含 ARM Cortex-A 的芯片)便宜得多。

- MicroBlaze 处理器本身是免费的,Xilinx 提供完整的开发工具链(Vitis IDE),无需支付额外的处理器授权费用,这对于成本敏感的项目至关重要。

-

高性能与低延迟:

- 由于处理器和其外设都在 FPGA 内部,数据传输速度极快,延迟极低,对于需要实时响应的应用(如电机控制、雷达信号处理),这是一个巨大优势。

- 可以创建自定义硬件加速器来处理特定算法(如 FFT、图像处理),然后将结果通过高速总线(如 AXI)传递给 MicroBlaze,这种“硬件加速 + 软件控制”的模式能实现远超通用处理器的性能。

-

快速原型验证:

在设计复杂的 ASIC 或 SoC 时,可以先在 FPGA 中集成 MicroBlaze 和所需的外设,搭建一个功能原型,用于验证软件算法和系统架构,大大缩短了开发周期。

-

完整的工具链支持:

- Xilinx 提供了强大的 Vitis IDE,集成了 GNU 工具链(编译器、链接器、调试器),支持 C/C++ 和汇编语言开发。

- 提供了丰富的 IP 核(如 AXI 总线、UART、SPI、I2C、DDR 控制器等),大大简化了系统设计。

- 内置了硬件调试器,支持 JTAG 在线调试。

局限性:

- 性能天花板:尽管性能很高,但其峰值性能和通用性无法与高端的 ARM Cortex-A/R 系列硬核处理器相比,它不适合运行大型操作系统(如 Linux)或需要极高计算密集度的通用任务。

- 开发复杂性:相比于在现成的开发板上直接运行 ARM 或 RISC-V,搭建一个基于 MicroBlaze 的系统需要具备 FPGA 和 SoC 设计的知识,包括 HDL、时序约束、总线协议等,门槛较高。

- 软件生态:MicroBlaze 主要运行轻量级实时操作系统,如 FreeRTOS、μC/OS-II 或裸机程序,其软件生态远不如 ARM 丰富,没有像 Android、Linux 这样的大型操作系统支持。

工作原理:如何构建一个基于 MicroBlaze 的系统?

一个典型的 MicroBlaze 系统并不是一个孤立的 CPU,而是一个复杂的 SoC,其构建过程如下:

-

创建处理器核:

- 在 Vivado/Vitis IDE 中,使用 IP Integrator 工具,从 IP 库中拖入一个 MicroBlaze IP 核。

- 在配置界面中,根据需求勾选或取消勾选功能,如:

- FPU (Floating-Point Unit):用于硬件浮点运算。

- MMU (Memory Management Unit):用于运行操作系统。

- ICache (Instruction Cache) 和 DCache (Data Cache):提升内存访问效率。

- 硬件断点:用于调试。

-

添加总线:

- MicroBlaze 系统的核心是 AXI (Advanced eXtensible Interface) 总线标准,Xilinx 提供了 AXI4、AXI4-Lite、AXI4-Stream 等多种总线。

- MicroBlaze 内部通过 AXI4-Lite 总线与简单的控制寄存器型外设(如 UART、Timer)通信。

- 通过 AXI4 总线与高性能外设(如 DDR SDRAM 控制器、DMA、自定义加速器)通信。

-

集成外设:

- 添加各种 IP 核作为 MicroBlaze 的外设,并通过 AXI 总线连接起来,常见的包括:

- Memory Controllers:用于连接 FPGA 外部的 DDR 内存。

- UART:用于串口通信,打印调试信息。

- Timer/Counter:用于定时和事件计数。

- GPIO:用于控制 LED 或读取按键。

- Ethernet MAC:用于网络通信。

- DMA Controller:实现内存到内存、内存到外设的高速数据搬运,解放 CPU。

- 添加各种 IP 核作为 MicroBlaze 的外设,并通过 AXI 总线连接起来,常见的包括:

-

中断系统:

- 外设(如 UART 接收到数据、Timer 溢出)可以通过 AXI Interrupt Controller IP 核向 MicroBlaze CPU 发送中断请求,实现异步事件处理。

-

软件编程:

- 使用 Vitis IDE 创建一个 C/C++ 应用工程。

- 编写应用程序,通过调用驱动程序(如 Xilinx 提供的

xil_printf,xuartps等)来操作硬件外设。 - 编译代码,生成可执行文件

.elf。 - 将

.elf文件与硬件设计一起下载到 FPGA 中运行。

应用场景

基于 MicroBlaze 的系统非常适合以下领域:

- 工业自动化与控制:电机控制、PLC、机器人控制,需要实时响应和硬件逻辑处理。

- 航空航天与国防:雷达信号处理、通信系统、加密解密,对可靠性和定制化要求极高。

- 医疗设备:医疗影像设备(如超声、MRI)的信号处理和实时控制。

- 高端消费电子:智能相机的图像处理、高端音频设备的数字信号处理。

- 通信设备:网络协议处理、数据包转发、基站部分功能。

- ASIC 原型验证:在流片前,用 FPGA 搭建包含 MicroBlaze 的原型,验证芯片的功能和性能。

与 RISC-V 的对比

这是一个非常热门的话题,两者都是可扩展的、开源的指令集架构,经常被放在一起比较。

| 特性 | MicroBlaze | RISC-V |

|---|---|---|

| 架构 | 专有架构,由 AMD Xilinx 拥有和控制。 | 开源架构,由 RISC-V 国际基金会管理,采用开放的许可模式。 |

| 实现方式 | 软核,需要开发者自己将其“放入”FPGA 中并构建完整系统。 | 软核 和 硬核 都有。 - 软核 (如 SiFive, PicoRV32) 可用于 FPGA。 - 硬核 (如 SiFive 的 Performance 系列) 作为独立芯片存在。 |

| 生态系统 | 成熟但封闭,与 Xilinx 的 FPGA 和 Vitis 工具链深度绑定,生态完整但局限于 Xilinx 平台。 | 快速开放,拥有庞大的全球社区和商业支持,正在形成从微控制器到高性能服务器的完整生态。 |

| 灵活性 | 高度可配置,但主要在 Xilinx 工具链内进行。 | 模块化设计,可根据标准规范(如 RV32I, RV64GC)自由组合扩展,灵活性理论上更高。 |

| 核心优势 | 与 FPGA 硬件的完美集成,在 Xilinx FPGA 内构建定制化 SoC 的最佳选择,工具链支持非常成熟。 | 开放标准,无厂商锁定,未来潜力巨大,适用于从 ASIC 到 FPGA 的各种平台。 |

| 选择建议 | 如果你的目标平台是 Xilinx FPGA,并且需要快速开发一个集成了大量定制硬件的 SoC,MicroBlaze 是一个非常成熟和高效的选择。 | 如果你追求开放标准、希望避免厂商锁定、计划在多个厂商(Intel, AMD, Xilinx 等)的 FPGA 上开发,或者计划开发自己的 ASIC,RISC-V 是更具前瞻性的选择。 |

MicroBlaze 是一款极其经典和成功的 FPGA 软核处理器,它凭借其高度灵活性、低成本、与 FPGA 硬件的深度集成能力,在过去十几年里成为了无数嵌入式系统设计的核心。

尽管如今 RISC-V 作为开源架构的兴起带来了新的竞争和选择,但 MicroBlaze 并没有过时,对于专注于 Xilinx FPGA 平台的开发者来说,MicroBlaze 依然是一个功能强大、工具链成熟、经过市场长期验证的可靠选择,它完美地诠释了“为特定应用而定制”的设计哲学,是 FPGA 领域不可或缺的关键 IP 核之一。